Наша прошлая статья подробно описала возможности процессорных архитектур ближайшего будушего. Они должны будут придти на смену современным Intel Core и AMD K8/K10 через полтора-два года. Однако сейчас уже ведутся более перспективные разработки, способные со временем вытеснить x86-архитектуру в принципе. Несколько лет назад Intel хотела проделать подобное представив процессор Itanium, но данную идею постигла неудача. Сейчас известно, что одной из очень перспективных разработок процессорного гиганта является проект Tera-scale. Недавно в его рамках был создан прототип 80-ядерного процессора, после чего его продемонстрировали широкой публике. В этой статье описывается устройство нового сверхпроизводительного чипа, а также перспективы начала его массового производства.

Наша прошлая статья подробно описала возможности процессорных архитектур ближайшего будушего. Они должны будут придти на смену современным Intel Core и AMD K8/K10 через полтора-два года. Однако сейчас уже ведутся более перспективные разработки, способные со временем вытеснить x86-архитектуру в принципе. Несколько лет назад Intel хотела проделать подобное представив процессор Itanium, но данную идею постигла неудача. Сейчас известно, что одной из очень перспективных разработок процессорного гиганта является проект Tera-scale. Недавно в его рамках был создан прототип 80-ядерного процессора, после чего его продемонстрировали широкой публике. В этой статье описывается устройство нового сверхпроизводительного чипа, а также перспективы начала его массового производства.

Недавно компания Intel обнародовала восемь новых технических документов о своем 80-ядерном процессорном прототипе Tera-scale, который является на сегодняшний момент одним из наиболее производительных решений в операциях с плавающей точкой. Первая информация об этой новой разработке компании Intel появилась весной прошлого года, а уже менее чем через год был продемонстрирован действующий прототип, преодолевший рубеж производительности в 1 TFLOPS. В этой статье мы попытались приоткрыть завесу тайны над потенциальной "убийцей" архитектуры x86 - платформой Tera-scale.

В настоящее время над проектом Tera-scale работают более 10 независимых команд специалистов Intel. Они занимаются проектированием и разработкой элементов новой платформы, начиная с электрических схем и заканчивая программным обеспечением.

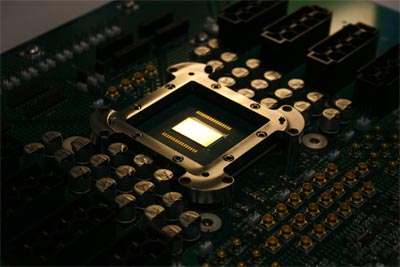

80-ядерный процессор в системной плате

Еще в феврале этого года, процессорный гигант представил прототип чипа, построенного в соответствии с 65 нм техпроцессом. Он объединял вместе 80 независимых ядер, и его частота составляла 3.16 - 5.80 ГГц. В шести различных тестах, отражающих производительность систем в традиционных вычислительных операциях, прототип процессора Tera-scale смог показать 1.01 TFLOPS параллельных вычислений при входной мощности всего лишь 62 Вт, 1.63 TFLOPS при частоте 5.10 ГГц и мощности 175 Вт, 1.81 TFLOPS при частоте 5.70 ГГц и мощности 265 Вт. Хотя эти результаты не могут не впечатлить, то, как этого добилась Intel, впечатляет еще больше.

Готовая логика

Инженеры Intel активно использовали уже готовые логические компоненты для создания своего прототипа. Это означает, что арифметические модули, контроллеры памяти, внутренние технологии маршрутизации, кэш-память и многие другие элементы прототипа были использованы либо в том же виде, в каком они уже имеются сейчас, либо же в них были внесены минимальные изменения. Этот подход позволил компании создать действующий прототип новой платформы менее чем за год. Впервые о проекте Tera-scale официально заговорили в марте 2006 года.

Сборная конструкция

Одним из наиболее существенных преимуществ платформы является ее "сборная конструкция". По сути Intel удалось создать процессор, для которого не важно какой вычислительный движок заключен в каждом из ядер. Это позволит в будущем, используя единую логическую систему, создавать сложнейшие вычислительные системы, которые будут собираться как "конструктор", для решения самых различных задач на базе одной платформы.

80 гомогенных ядер прототипа Tera-scale

Это стало возможным благодаря использованию новой шинной архитектуры, позволяющей любому ядру связываться напрямую с любым другим ядром по методу "один к любому". Сам по себе прототип использует 80 однородных ядер, но, по заявлению специалистов компании, число используемых ядер не ограничено, и они отнюдь не должны быть однородными.

Связь с ядрами

Intel использует многоуровневую коммуникационную систему в своей платформе Tera-scale. Представленный прототип чипа состоит из десяти блоков (узлов), каждый из которых включает по восемь ядер. В свою очередь каждый узел может обращаться к любому другому узлу и затем уже к любому ядру, входящему в его состав, в пределах процессора. Каждое ядро напрямую может обращаться к любому ядру из своего узла, но требует использования связи "узел-к-узлу" при обращении к ядрам за пределами своего узла. По словам представителей процессорного гиганта, подобная система маршрутизации, применяемая в Tera-scale, позволяет любому элементу в пределах узла связываться с любым элементом на чипе.

При этом отмечается, что этими элементами не обязательно должны быть вычислительные ядра. По сути, в рамках одного узла могут быть объединены разнородные ядра. При этом сам узел не обязан содержать что-либо кроме системы коммуникационного маршрутизатора. Это означает, что платформа Tera-scale позволяет совершенно без ограничений объединять в рамках чипа цифровые процессоры сигналов, вычислительные ядра или другие элементы.

Таким образом компании удалось создать на одном чипе в полном смысле "многокомпьютерную" систему, способную решать разноплановые задачи в зависимости от используемых элементов этого "конструктора". Если вам нужна более производительная в операциях с плавающей точкой система - пожалуйста, размещайте дополнительный узел с ядрами, занимающимися вещественными вычислениями. Или же можно добавить несколько специализированных RISC-ядер или узел кэш-памяти. Такая сборная структура открывает перед нами новые возможности и гибкость по настройке производительности системы, которые даже трудно сейчас представить.

Исполнение

Структура Tera-scale представляет собой своеобразный "сэндвич". Память размещена в нижней части чипа и вертикально связанна с находящимся сверху ядром. Каждому ядру полагается по 64 Мбайт ОЗУ. В прототипе общий объем памяти составил 5.12 Гбайт, но Intel была ограничена техническими требованиями и определенным количеством транзисторов.

Коммуникационная система была создана чрезвычайно быстро благодаря использованию уже готовых компонентов Intel. Это хотя и несколько ограничило пропускную способность шины, которая без сомнения будет гораздо выше в финальном исполнении процессоров Tera-scale, тем не менее, прототип продемонстрировал впечатляющую внутреннюю пропускную способность 1.2 Тбайт/с.

Также на прототипе была реализована "экономная" система дистрибьюции сигнала синхронизации. По данным специалистов Intel около 30% всего энергопотребления процессора идет на эту операцию, а у Tera-scale это лишь 10%, что достигается благодаря меньшему числу повторов. Это позволяет передавать сигналы на большие расстояния с меньшими энергозатратами. Для этого компании пришлось преодолеть серьезную проблему в виде несовпадения фаз исходного и полученного сигнала при передаче сигналов на большие расстояния. Решение помогла найти математика: рассчитывается на сколько может измениться фаза сигнала синхронизации при передаче на определенные расстояния. Это позволяет изначально изменить передаваемый сигнал, чтобы в конечную точку он "прибыл" в нужной фазе.

Маршрутизация

Еще одной замечательной стороной новой платформы является маршрутизация. Каждое ядро само по себе снабжено маршрутизатором, который может передавать сигналы в шести направлениях. Это традиционные север, юг, восток и запад, позволяющие восьми ядрам обращаться к соседям. Есть еще два дополнительные направления: логические вверх и вниз, которые связаны с обращениями к памяти и узлу.

Каждое ядро обращается напрямую к соседним ядрам. Также напрямую связываются и узлы друг с другом. При этом совершенно не важно, что находится в узлах, главное, что они могут друг с другом общаться. А с системой маршрутизации, используемой здесь, это не составляет особого труда. Так Intel реализовала в Tera-scale масштабируемость, позволяющую создавать сколь угодно сложные вычислительные системы.

Система маршрутизации, реализованная в прототипе Tera-scale, позволяет настраивать физические пути передачи данных после отправки первоначального запроса. Когда путь открыт, отправитель передает N-число пакетов данных. После приема информации получатель посылает обратно сигнал о том, что передача прошла успешно без ошибок, после чего закрывается путь. В этом случае каждый маршрутизатор между отправителем и получателем точно знает сколько данных будет передано. И после того, как информация передана, роутеры могут автоматически перестроиться для отправки данных в соответствии со следующим заданием.