Наша прошлая статья подробно описала возможности процессорных архитектур ближайшего будушего. Они должны будут придти на смену современным Intel Core и AMD K8/K10 через полтора-два года. Однако сейчас уже ведутся более перспективные разработки, способные со временем вытеснить x86-архитектуру в принципе. Несколько лет назад Intel хотела проделать подобное представив процессор Itanium, но данную идею постигла неудача. Сейчас известно, что одной из очень перспективных разработок процессорного гиганта является проект Tera-scale. Недавно в его рамках был создан прототип 80-ядерного процессора, после чего его продемонстрировали широкой публике. В этой статье описывается устройство нового сверхпроизводительного чипа, а также перспективы начала его массового производства.

Наша прошлая статья подробно описала возможности процессорных архитектур ближайшего будушего. Они должны будут придти на смену современным Intel Core и AMD K8/K10 через полтора-два года. Однако сейчас уже ведутся более перспективные разработки, способные со временем вытеснить x86-архитектуру в принципе. Несколько лет назад Intel хотела проделать подобное представив процессор Itanium, но данную идею постигла неудача. Сейчас известно, что одной из очень перспективных разработок процессорного гиганта является проект Tera-scale. Недавно в его рамках был создан прототип 80-ядерного процессора, после чего его продемонстрировали широкой публике. В этой статье описывается устройство нового сверхпроизводительного чипа, а также перспективы начала его массового производства.

Самокоррекция

В Tera-scale реализована мощная система самокоррекции, столь необходимая при создании многоуровневых сложных вычислительных систем. В том случае, если ядро не проходит по каким-либо причинам самоконтроль, оно может отправить другим ядрам информацию о своем выходе из строя. При этом система маршрутизации автоматически перестроится в соответствии с "внесенными" изменениями и тем самым не потребуется программное вмешательство. Это позволит процессорам на платформе Tera-scale продолжать корректное функционирование, даже если часть вычислительных ядер вышла из строя.

Также предусмотрена возможность перераспределения потоков обрабатываемых данных по наиболее эффективным "маршрутам". По словам инженеров процессорного гиганта, эта технология позволяет более эффективно управлять терморегуляцией, распределением загрузки кэша и др. Так, например, "переброска" потоков информации подальше от наиболее "горячих" узлов позволит снизить локальный нагрев и тем самым повысить эффективность теплоотвода, а также использовать свободную кэш-память.

Таким образом полностью автоматизированная система маршрутизации может справиться с перераспределением любых потоков данных. При этом для внешнего программного обеспечения ничего не изменяется - ОС продолжает думать, что задачу выполняет ядро №1, когда эта задача возложена уже на ядро №4. Значение подобной автоматической подстраховки сложно переоценить, особенно если она не сказывается негативно на производительности системы в целом.

Архитектура кэш-памяти

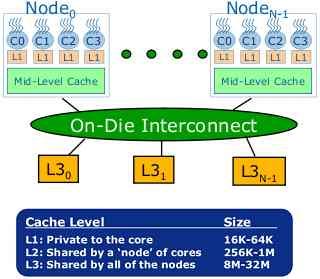

В процессорах на платформе Tera-scale предусмотрено использование трехуровневой системы кэширования. Кэш L1 будет непосредственно связан с каждым ядром и его объем составит 16-64 Кбайт. Кэш второго уровня размером 256-1024 Кбайт будет уже общий для всего узла. Доступным для всех узлов станет кэш третьего уровня объемом 8-32 Мбайт. Модули кэш-памяти будут размещаться на той же подложке, что и вычислительные ядра, маршрутизаторы и прочие элементы.

Структура кэш-памяти Tera-scale

Также инженеры Intel продемонстрировали модель работы нового L4-кэша высокой емкости, который будет размещаться между процессором и памятью (схема "бутерброд"). Есть также вариант размещения кэша четвертого уровня напротив процессора. У обеих схем есть свои преимущества и свои недостатки. В настоящее время эксперты компании тестируют оба варианта.

Варианты расположения кэша L4

Еще одним важным элементом системы кэширования станет управление приоритетами выполняемых задач, реализуемое посредствам настроек QoS (Quality of Service). По данным, обнародованным представителями процессорного гиганта, благодаря внедрению QoS удается достичь 10-20% прироста производительности над системой работающей по классической схеме "первый пришел, первым обслужен". Всегда есть задачи, требующие более высокого приоритета доступа к данным, и если система установки приоритета их верно идентифицирует, то работа в целом выполняется быстрее.

Процесс разработки

По словам авторов платформы Tera-scale, при ее разработке главным критерием были требования, предъявляемые программным обеспечением в будущем, к аппаратной части. Предстояло ответить не только на вопрос "что будет нужно", но и "как этого добиться".

В ходе проектирования и создания прототипа чипа Tera-scale использовались симуляторы циклов, FPGA эмуляторы и реальные кремниевые прототипы. Процесс разработки новой платформы инженерами Intel был организован в виде последовательного проектирования "на бумаге", создания прототипа, тестирования его, внесения изменений в программное обеспечение и затем пересмотра "бумажного" проекта, после чего цикл начинался заново.

Будущее

В представленном прототипе наибольший интерес, бесспорно, представляет многоуровневая структура и использование уже имеющихся ядер в узлах. Схожая структура будет реализована в процессорах AMD Fusion, объединяющих на одной подложке общие вычислительные функции с проектированием геометрических поверхностей и иными функциями современных GPU. По словам представителей компании Intel в рамках узла платформы Tera-scale может быть реализована логика GPU. Это же касается и таких мощных графических чипов как ClearSpeed CSX600. Даже DSP, Gigabit Ethernet, полноценные видео решения, большая часть системной логики и многое другое. Любой тип кремниевых продуктов, существующих на сегодняшний день, может быть внедрен в эту модель, по крайней мере в теории.

В принципе ничто не мешает использовать в чипе Tera-scale даже ядра c различной иной разрядностью. Благодаря этому разработанная Intel платформа откроет ранее недоступные возможности виртуализации и оптимизации системы под конкретные задачи. В ходе демонстрационного тестирования процессорный гигант показал, что одному чипу Tera-scale под силу заменить коммерческую компьютерную систему, состоящую из 63 системных блоков, включающих 130 процессоров.

По словам представителей Intel, инженерам компании удалось очень многого добиться в кратчайшие сроки. Но при этом остается много препятствий, которые еще предстоит преодолеть, перед тем как запустить процессоры на платформе Tera-scale в серию. Пока не называется даже предварительная дата появления подобных решений на рынке, но, по словам экспертов, программное обеспечение, которое сможет в полной мере использовать возможности чипов Tera-scale, увидит свет лишь через 5-10 лет. Поэтому очевидно, что Intel и будет ориентироваться на эти сроки и вычислительных систем на базе этой новой платформы не стоит ждать раньше 2012-2013 года.

Эпилог

Intel Tera-scale является чрезвычайно гибкой и перспективной платформой, которая в будущем может ознаменовать начало новой вехи в компьютерном проектировании, открывающей недоступные доселе возможности. Эта технология позволит выполнять огромное количество параллельных операций в рамках модели MIMD (Multiple Instruction, Multiple Data). И это можно будет реализовать, используя традиционную многоядерную модель или через добавление специализированных ядер.

В перспективе процессоры Intel Tera-scale могут стать не только сверхпроизводительными процессорами с низким энергопотреблением, но и стать наследниками архитектуры x86, которая рано или поздно уступит свое место более современной разработке.

По материалам ресурса TGDaily